# ARTIFICIAL INTELLIGENCE AT THE EDGE

A JOINT EUROPEAN ROADMAP FOR EDGE AI

October 2025

### **IMPRINT**

### EPoSS e. V. European Association on Smart Systems Integration

Steinplatz 1, 10623 Berlin, Germany

www.smart-systems-integration.org

#### Layout

Juliane Lenz – Berlin, Germany

### Contact

Inessa Seifert – VDI/VDE Innovation + Technik GmbH | EPoSS Inessa.Seifert@vdivde-it.de

## **Content**

| 1 | Introduction                                                                                | 5             |

|---|---------------------------------------------------------------------------------------------|---------------|

| 2 | Evolving Cloud-Edge-IoT Infrastructures and Data-driven Value Cha                           | n <b>in</b> 7 |

| 3 | AI and Edge AI Development Trends: Setting the Scene                                        | 10            |

|   | 3.1 Most discussed Edge AI topics                                                           | 10            |

| 4 | Overview of New Hardware Architectures                                                      | 13            |

|   | 4.1 SNN-based accelerators                                                                  | 13            |

|   | 4.2 RISC-V based accelerators                                                               | 14            |

|   | 4.3 Photonic/optical-based accelerators                                                     | 15            |

|   | 4.4 Biological processors                                                                   | 16            |

|   | 4.5 Chiplets                                                                                | 17            |

|   | 4.6 In-memory computing (memristive technologies)                                           | 17            |

|   | 4.7 ASICs, SoCs and microcontrollers                                                        | 18            |

|   | 4.8 FPGAs                                                                                   | 18            |

|   | 4.9 ECHO gateway for AI processing                                                          | 19            |

|   | 4.10 Conclusion                                                                             | 20            |

| 5 | Challenges, Constraints and Limitations Drive Innovation in Hardware Solutions for Edge AIs | 22            |

|   | 5.1 Edge device constraints                                                                 | 22            |

|   | 5.2 Edge model and application constraints                                                  | 23            |

|   | 5.3 Environmental, operating and financial constraints                                      | 24            |

|   | 5.4 Safety, security and privacy technologies                                               | 25            |

|   | 5.5 Technology challenges for computation                                                   | 25            |

|   | 5.6 Memory wall challenges                                                                  | 26            |

|   | 5.7 Energy efficiency                                                                       | 26            |

|   | 5.8 Modularity and interoperability of the technology stack                                 | 27            |

|   | 5.9 Software and data challenges in on-device trainings                                     | 27            |

|   | 5.10 Engineering tools for designing Edge AI-driven products                                | 28            |

|   | 5.11 Conclusion: Challenges driving innovation in Edge AI hardware                          | 30            |

| MultiSpin.Al: An Opportunity for Europe to  Lead the Field of Edge AI Computation Hardware |                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 6.1                                                                                        | Requirements on Edge AI hardware driving innovation in spintronics             | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 6.2                                                                                        | Spintronic AI platforms                                                        | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 6.3                                                                                        | Comparison of Edge AI hardware platforms                                       | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 6.4                                                                                        | MultiSpin.AI: A paradigm shift in Edge AI processing                           | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 6.5                                                                                        | Sustaining the future of spintronic AI hardware                                | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 6.6                                                                                        | Conclusion                                                                     | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

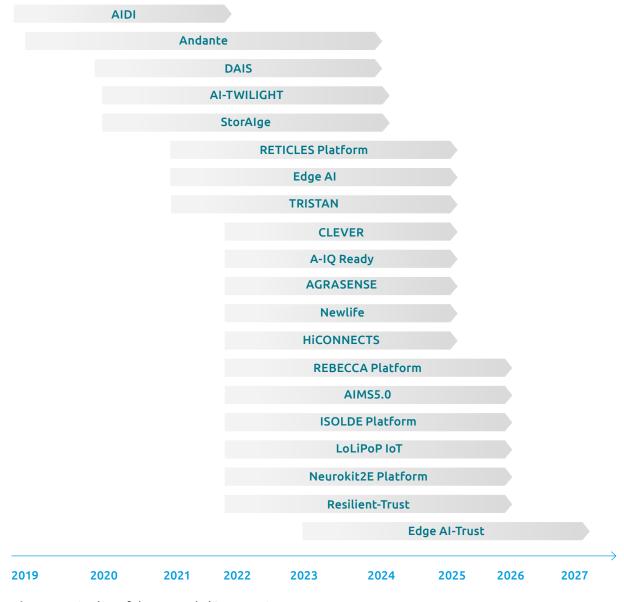

| KD                                                                                         | T and Chips JU Research and Innovation Timeline                                | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 7.1                                                                                        | Data collection                                                                | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 7.2                                                                                        | Design hardware platforms, engineering tools and ecosystems                    | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| Ma                                                                                         | rket Dynamics                                                                  | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| Go                                                                                         | als, Objectives and Recommendations for Action                                 | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 9.1                                                                                        |                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 9.2                                                                                        | vendors to system integrators, along with collaboration across EU stakeholders | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 9.3                                                                                        | ·                                                                              | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| Aul                                                                                        | thors                                                                          | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| EVIA                                                                                       | ATIONS                                                                         | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| OF FI                                                                                      | GURES AND TABLES                                                               | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|                                                                                            | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>KD<br>7.1<br>7.2<br>Ma<br>9.1<br>9.2 | Lead the Field of Edge AI Computation Hardware  6.1 Requirements on Edge AI hardware driving innovation in spintronics 6.2 Spintronic AI platforms 6.3 Comparison of Edge AI hardware platforms 6.4 MultiSpin.AI: A paradigm shift in Edge AI processing 6.5 Sustaining the future of spintronic AI hardware 6.6 Conclusion  KDT and Chips JU Research and Innovation Timeline 7.1 Data collection 7.2 Design hardware platforms, engineering tools and ecosystems  Market Dynamics  Goals, Objectives and Recommendations for Action  9.1 Objective 1: Create European ecosystem and enforce synergies between existing ecosystems for fast adoption of Edge AI solutions  9.2 Objective 2: Foster collaboration along the AI value chain in Europe, from chip |  |  |

## 1 Introduction

In recent years, digitalisation, the availability of data and the possibilities for applying Artificial Intelligence (AI) have become important business drivers for Europe's key industrial sectors. In our understanding, AI is a technical system that has the ability to mimic human intelligence, which is characterised by behaviours such as sensing, learning, understanding, decision-making and acting. Due to the availability of powerful computing hardware (graphics processing units (GPUs) and specialised architectures) and large amounts of data, AI solutions – in particular Machine Learning (ML), and more specifically Deep Learning (DL) – have found numerous and widespread applications over the last two decades (including image recognition, fault detection and automated driving functions).

Low latency, privacy, connectivity limits and distributed applications have driven research in Edge AI, which enables processing and decision-making near data sources – across cloud, edge, and Internet of Things (IoT) devices. It involves training AI models in the cloud and deploying them on edge devices.

In 2021, the EPoSS Edge AI Working Group published a white paper called "AI at the Edge" [1], which provided a broad overview of AI methods and techniques, together with technological milestones to guide the research and innovation over the next few years.

Following the publication of this white paper, two industry associations – EPoSS and INSIDE – joined forces. The joint Edge AI Working Group is a community of hardware and software experts from industry and academia who drive research and innovation for both national and EU-funded projects, and contribute their insights and views concerning the future of Edge AI.

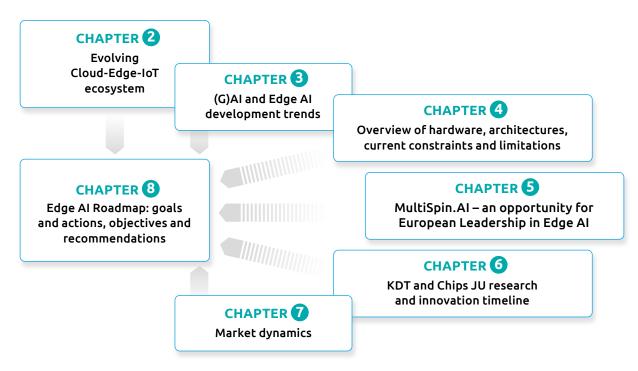

Recent breakthroughs, and in particular in the domain of Generative AI (GenAI), have driven a clear need to revise our roadmap, including the technology milestones, to better understand and exploit the potential of GenAI in the computing continuum, including at the edge. *Figure 1.1* shows how to read our refined and updated Vision.

<sup>1</sup> EPoSS Whitepaper, 2021, "Al at the Edge" (available at https://www.smart-systems-integration.org/publication-eposs-ai-white-paper)

Figure 1.1: How to read this document

This white paper begins with an overview of the evolving cloud-edge-IoT ecosystem, highlighting the critical role of intelligent, resource-constrained devices that interact with both humans and machines. *Chapter 3* then explores the current AI trajectory, including the five levels of Artificial General Intelligence (AGI) coined by OpenAI CEO Sam Altman<sup>[2]</sup>. *Chapter 4* dives into cutting-edge hardware architectures, while *Chapter 5* examines the many challenges, constraints and limitations around innovation in hardware for Edge AI development. *Chapter 6* introduces a novel spintronics-based solution that addresses the memory-wall issue with impressive energy efficiency and performance. *Chapter 7* outlines the timeline and expected outcomes of KDT and Chips Joint Undertaking (Chips JU) projects in the coming years. *Chapter 8* analyses global market trends, spotlighting Europe's Edge AI landscape and NVIDIA's growing dominance in the ecosystem. The final chapter outlines important goals, objectives and recommendations for action that will boost the competitiveness of European companies, building on the insights from earlier chapters.

<sup>2 &</sup>lt;u>https://www.forbes.com/sites/jodiecook/2024/07/16/openais-5-levels-of-super-ai-agi-to-outperform-human-capability</u>

## 2 Evolving Cloud-Edge-IoT Infrastructures and Data-driven Value Chains

The distributed and resource-constrained nature of edge computing presents challenges that are different from those of centralised computing. Deploying AI on edge devices presents significant technical challenges, largely due to heterogeneity: the variety of hardware platforms, real-time operating systems, sensor types, and AI workloads. While classic AI is now effectively deployed at the edge, GenAI has introduced new complexities. From around 2014 with the rise of Generative Adversarial Networks (GANs) and popularised by breakthroughs such as Transformers (2017), GenAI workloads have become increasingly hyperparameterised and resource-intensive.

The findings collected in the study "Transitioning from TinyML to Edge GenAI: A Review" underscore the growing interest in deploying Edge GenAI models specifically on smartphones. For instance, imagine a hypothetical service designed specifically for Gen Z smartphone users. It comes with a USD15 monthly subscription and sets a strict performance expectation: latency must not exceed five seconds. Meeting these demands at scale presents significant challenges, raising questions about the readiness of the current infrastructure for widespread deployment.

A case study with Qwen2-VL-7B-Instruct<sup>[4]</sup>, a cutting-edge multimodal GenAI model, highlights some of the key scalability challenges. With modest usage assumptions (60 tokens per user per query, and a five-second latency limit), serving all 5.16 billion smartphone Gen Z users would demand:

- over 40,000 AI superclusters (each on the scale of NVIDIA's Cortex AI cluster [5]);

- power infrastructure of up to 130 MW per cluster; and

- unfeasible levels of acceleration and cost.

In short, large-scale GenAI deployment via the cloud is neither economically nor environmentally sustainable. However, for training GenAI models, cloud computing remains essential; to preserve data privacy and sovereignty, on premises AI training is also a promising direction to attain some relief from cloud dependency.

<sup>3 &</sup>lt;u>https://www.mdpi.com/2504-2289/9/3/61</u>

<sup>4 &</sup>lt;a href="https://huggingface.co/Qwen/Qwen2-VL-7B-Instruct">https://huggingface.co/Qwen/Qwen2-VL-7B-Instruct</a>

$<sup>\</sup>begin{tabular}{ll} 5 & $https://technologymagazine.com/ai-and-machine-learning/a-first-look-at-elon-musks-new-cortex-ai-supercluster (a) & $https://technologymagazine.com/ai-and-machine-learning/a-first-look-at-elon-musks-new-cortex-ai-supercluster (a) & $https://technologymagazine.com/ai-and-machine-learning/a-first-look-at-elon-musks-new-cortex-ai-supercluster (b) & $https://technologymagazine.com/ai-and-machine-learning/a-first-look-at-elon-musks-new-cortex-ai-supercluster (b) & $https://technologymagazine.com/ai-and-machine-learning/a-first-look-at-elon-musks-new-cortex-ai-supercluster (c) & $https://technologymagazine.com/ai-and-machine-learning/ai-and-machine-learning/ai-and-machine-learning/ai-and-machine-learning/ai-and-machine-learning/ai-and-machine-learning/ai-and-machine-learning/ai-and-machine-learning/ai-and-machine-learning/ai-and-machine-learning/ai-and-machine-learning/ai-and-machine-learning/ai-and-machine-learning/ai-and-machine-learning/ai-and-machine-learning/ai-and-machine-learning/ai-and-machine-learning/ai-and-machine-learning/ai-and-machine-learning/ai-and-machine-learning/ai-and-machine-learning/ai-and-machine-learning/ai-and-machine-learning/ai-and-machine-learning/ai-and-machine-learn$

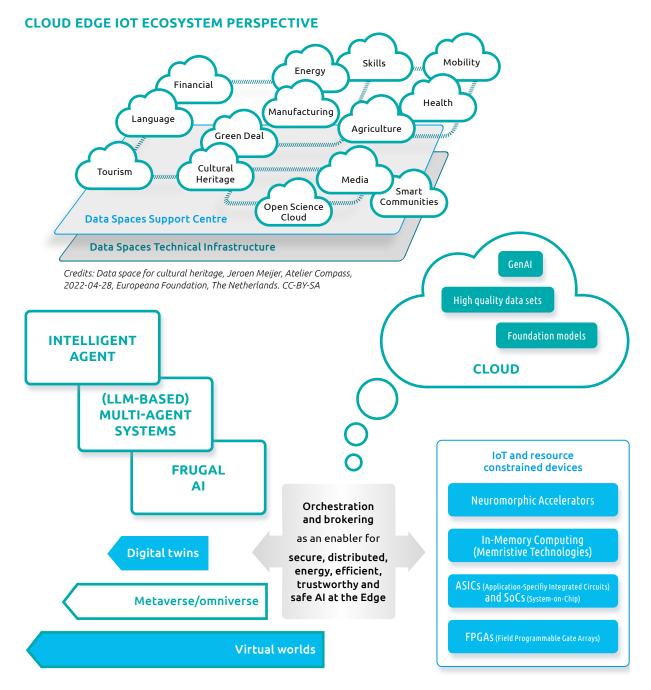

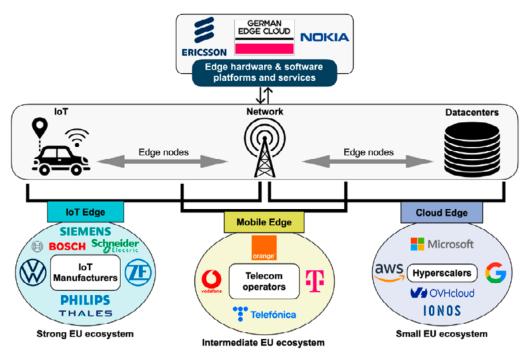

Figure 2.1: Cloud-Edge-IoT ecosystem view

In Edge AI systems, data is both collected and processed locally at or near the edge of the network, leveraging IoT devices and resource-constrained hardware. Cloud-edge-IoT infrastructures must be highly adaptable to accommodate varying data volumes, velocities, and privacy and security requirements. The data journey begins with collection at tiny sensors, data generators, and micro-devices. Based on the application's needs and privacy considerations (see Table 7.1), the data is either processed locally or transferred to cloud or high-performance computing infrastructures for advanced optimisation and decision-making tasks.

The tech stack for data-driven Edge AI consists of several interconnected layers that enable the collection, processing and application of data. The key building blocks include the following.

- GenAI, foundation models, high-quality datasets and data spaces: Robust AI solutions at the edge rely

on foundation models and high-quality datasets. Common European Data Spaces offer the infrastructure

for federated, distributed sharing of these datasets.

- Multi-agent systems: Powered by specialised Large Language Models (LLMs) and foundation models, these agents deliver high performance while being optimised for resource-constrained devices such as smartphones. They enable advanced AI functionalities directly at the edge.

- Digital twins, metaverse/omniverse, and virtual worlds: Virtual models of physical objects use realtime sensor data to simulate behaviour, monitor operations, and optimise performance throughout their lifecycle.

- **Neural architecture search:** To automatically devise AI models to solve edge problems by leveraging on-premises AI energy-efficient computing and data availability.

- **Orchestration and brokering:** Automating the configuration, management and coordination of systems, applications, services and devices for streamlined operations.

- **Trust and security:** Incorporating software and hardware components to ensure system reliability, privacy, robustness, dependability, safety and performance, all critical for secure deployments.

Each of these building blocks represents an innovation area together with market opportunities, with emerging or established players driving innovation to accelerate Edge AI adoption across the computing continuum.

The broader view aims to illustrate key interactions within the ecosystem, revealing the complexity of dependencies together with associated challenges and potential risks. In this context, *Chapter 4*, "Overview of New Hardware Architectures", focuses on the specific challenges of running Edge AI on resource-constrained devices. This ecosystem perspective offers a strategic lens to understand the research and innovation activities of KDT and Chips JU projects described in *Chapter 7*, as well as market structure with the positioning of dominant players explored in *Chapter 8*. The next chapter, "AI and Edge AI Development Trends: Setting the Scene", explores the evolution of AI, highlighting key trends that are shaping the future of innovation in Edge AI.

## 3 AI and Edge AI Development Trends: Setting the Scene

## 3.1 Most discussed Edge AI topics

AI is the most rapidly developing technologies that is affecting and challenging the current technological landscape. According to Gartner's Hype Cycle<sup>[6]</sup>, Edge AI has surpassed its peak and is expected to reach a "plateau of productivity" within two years. This signifies the technology's transition through its initial phases of hype, disillusionment and experimentation, ultimately becoming a standard and reliable tool for various use cases. Furthermore, according to the Bank of America, the Taiwan Semiconductor Manufacturing Co (TSMC) will enable USD1 trillion in manufacturing digital chips by 2030<sup>[7]</sup> for its driving customers through AI computer servers, including on-premises AI, Edge AI, tiny, and in particular agentic, including humanoid robots<sup>[8]</sup>.

GenAI introduces new challenges, particularly in the context of distributed computing environments. The training of generative AI models, especially LLMs, requires a huge amount of computing power and energy, usually provided by cloud computing infrastructures and efficient data centres. According to Yann LeCun, modern LLMs are trained with 20 trillion tokens, with each token comprising three bytes – so that's 10<sup>14</sup> tokens! In the first four years of life, the brain receives 16,000 hours of visual information at 2 MB/s. This is the equivalent amount of information needed to train an LLM. Therefore, for the foreseeable future, we will be very far (perhaps light years) from achieving superhuman intelligence. It remains to be seen what computing and energy resources would be required to power such a computer should humanity ever reach that point.

High-quality datasets are fundamental to the training of LLMs as they ensure the development of accurate, unbiased and comprehensive representations of language. These datasets minimise the propagation of errors and biases, thereby enhancing the model's generalisation capabilities and reliability. High-quality data collected from IoT devices and sensor networks reduces noise during training, enabling the model to focus on meaningful patterns and relationships for more efficient learning. This ensures that LLMs achieve higher performance, particularly in real-world applications and complex tasks requiring contextual understanding and domain-specific expertise. Consequently, the quality of training data directly influences the trustworthiness, applicability and ethical deployment of LLMs across diverse fields. The objective of Common European Data Spaces<sup>[9]</sup> is to establish uniform data infrastructures and governance frameworks that enable data pooling, access and sharing. This allows them to provide high-quality resources for data-driven AI-based applications.

The recent breakthroughs in AI technologies have had a significant impact on the technology landscape. The most intensively discussed areas in the Edge AI community are currently the following.

- **LLMs** enable machines to understand, reason and generate human-like language, revolutionising natural language processing (NLP) tasks.

- **GenAI** enables the creation of novel content such as images, music and text using advanced transformer and other architectures of generative models.

<sup>6</sup> https://www.gartner.com/en/articles/hype-cycle-for-artificial-intelligence

<sup>7</sup> https://www.investing.com/news/stock-market-news/how-tsmc-is-enabling-1-trillion-semiconductor-era-4010839

<sup>8</sup> https://www.forbes.com/sites/johnkoetsier/2025/04/30/humanoid-robot-mass-adoption-will-start-in-2028-says-bank-of-america

<sup>9</sup> https://digital-strategy.ec.europa.eu/en/policies/data-spaces

- Responsible AI focuses on building trustworthy AI systems that prioritise ethical decision-making, fairness

and societal well-being. It also promotes transparency and accountability in AI processes. However, it

requires the creation of governance frameworks and regulatory policies to align AI development with the

principles of responsibility, sustainability and social impact.

- Multi-agent AI systems (MAS) are composed of multiple intelligent agents that can sense, search

information, learn and act autonomously to achieve individual and collective goals. Powered by artificial

reasoning intelligence, these systems demonstrate building sequences of thought capabilities by being

flexible, scalable and robust to enable broader real-world impact across industries. MAS involve multiple

interacting agents software or hardware entities that work together to solve complex problems

beyond their individual capabilities.

- **Embodied (physical) AI** refers to the use of AI techniques to solve problems that involve direct interaction with the physical world for example, by observing the world through sensors or modifying the world through actuators. It integrates AI into physical systems, and is increasingly combined with digital twins and simulations to improve performance and decision-making in various industries.

- Al and quantum computing is still an emerging technology, promising breakthroughs in optimisation, cryptography and drug discovery through quantum speed-ups. It has accelerated the need for hybrid Alquantum algorithms, and novel computational and open programming frameworks.

One of the most debated emerging topics in AI is **Artificial General Intelligence (AGI)**<sup>[10]</sup>. According to Gartner, AGI refers to AI that can understand, learn and apply knowledge across a wide range of tasks and domains. Unlike narrow AI, which is designed for specific applications, AGI possesses cognitive flexibility, adaptability and general problem-solving skills.

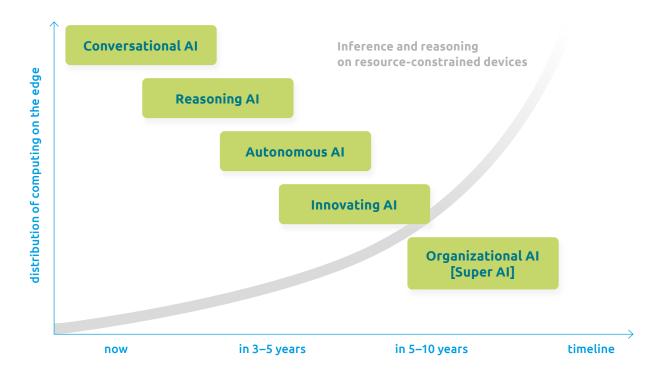

AGI is defined as AI capable of surpassing human performance in most tasks. Sam Altman, CEO of Open AI, a leading force in GenAI and the creator of ChatGPT, uses a **five-tier scale** to measure progress toward this goal [11]:

- **1. Conversational AI (current stage):** At this level, AI interacts with users in natural language. Think of customer service chatbots, AI writing assistants such as ChatGPT, or AI coaches. Most businesses today leverage AI at this stage.

- **2. Reasoning AI (near future):** This stage introduces "reasoners" that is, AI capable of sequences of thought to achieve problem-solving at a level comparable to a PhD graduate, but without external tools.

- **3. Autonomous AI:** Here, AI "agents" can operate independently for days, managing tasks without human intervention. Unlike today's automations, which require monitoring, future AI at this level will be self-correcting, ensuring reliability with minimal oversight. This may include autonomous learning, in addition to inference.

- **4. Innovating AI:** Known as "innovators", these systems go beyond executing tasks they improve them. Instead of just following rules, they critically analyse processes to enhance efficiency and effectiveness.

- **5. Organisational AI (super AI):** At the final stage, AI functions as an entire organisation, managing all roles, optimising processes and collaborating autonomously without human involvement.

He predicts we could reach level five within **10 years** (see *Figure 3.1*), while others estimate it may take up to **50 years**. The exact timeline remains uncertain, but the rapid pace of AI advancement is undeniable.

<sup>10 &</sup>lt;u>https://www.gartner.com/en/information-technology/glossary/artificial-general-intelligence-agi</u>

<sup>11 &</sup>lt;a href="https://www.forbes.com/sites/jodiecook/2024/07/16/openais-5-levels-of-super-ai-agi-to-outperform-human-capability">https://www.forbes.com/sites/jodiecook/2024/07/16/openais-5-levels-of-super-ai-agi-to-outperform-human-capability</a>

Figure 3.1: Timeline with evolving AI trends with implications on Edge AI

**GenAI** will inevitably have a significant impact on Edge AI that will bring real-time decision-making capabilities to resource-constrained devices such as IoT, sensors and smartphones. It will push advances in hardware optimisation and lightweight AI models to reshape edge computing paradigms. The rapid progress of GenAI presents both challenges and opportunities for the semiconductor research and innovation community, requiring a strategic reassessment of its R&I trajectory.

## 4 Overview of New Hardware Architectures

Deep Neural Network (DNN) algorithms achieve high-performance results for various applications – autonomous driving, smart health, smart home, smart agriculture, etc. However, these algorithms require high computational power for both training and inference. The field of high-performance DNN accelerators has been largely dominated by cloud platforms using NVIDIA GPUs and Google tensor processing units (TPUs), and the general trend has been to provide flexibility and performance to serve a wide range of DNN applications – without much concern for power consumption.

In contrast to monolithic accelerators such as the Google TPU, GPUs are modular by design and hence can scale from high-performance computing systems to edge devices. For example, NVIDIA's Ampere microarchitecture powers big A100 cores in data centres but also the Jetson Orin chips. A similar approach is taken by AMD, whose AI Engine Architecture is a scalable array of vector processors that accelerates AI inference workloads in laptop chips, 5G/6G communication infrastructure, as well as automotive edge devices. The advantage of edge and smart sensor AI solutions is the use of inference accelerators for tiny neural network models that offer low power, high throughput and low latency, opening up the possibility of moving processing closer to the sensor and sensor nodes.

#### 4.1 SNN-based accelerators

Spiking Neural Networks (SNNs) represent an evolution in artificial neural networks (ANNs) incorporating principles inspired by the workings of biological brains. Unlike ANNs, which process data continuously, SNNs utilise discrete spikes as communication signals, introducing a time dimension to neuron activity. This makes SNNs uniquely capable of modelling the temporal dynamics of biological neurons, such as the timing of spikes and inter-neuronal dependencies. By leveraging event-driven computation, SNNs achieve remarkable energy efficiency, particularly when implemented on specialised neuromorphic hardware like Intel's Loihi or IBM's TrueNorth.

In neuromorphic hardware, their efficient computation paradigms make them ideal for low power environments such as edge devices. In robotics and sensory processing, their capacity for real-time, temporal pattern recognition allows for advanced control systems and adaptive behaviours. There are also applications in fields such as autonomous systems, speech recognition and time-series analysis, where SNNs can naturally encode and process sequential data. Despite their flexibility, SNNs adoption presents challenges such as the complexity of training methods, the need for specialised hardware, and difficulties in analysing their temporal activity patterns. Training SNNs is currently a complex task, often relying on approximations or hybrid approaches involving traditional neural networks.

SNNs require specialised hardware to fully realise their potential, as general-purpose GPUs or CPUs struggle with the sparse and temporal nature of spiking activity. SNN accelerators are designed to efficiently handle SNN highly parallel event-driven operations and temporal characteristics, with the advantage of energy efficiency and low-latency computation. Chips like Intel's Loihi and IBM's TrueNorth have set benchmarks in this field by integrating programmable synaptic plasticity, on-chip learning, and support for large-scale spiking networks. Intel's Loihi, for example, has pioneered the inclusion of biologically inspired learning rules such as Spike-Timing-Dependent Plasticity (STDP), enabling real-time adaptability. Similarly, IBM's TrueNorth chip offers ultra-low power operation with its million-neuron architecture, demonstrating the scalability of neuromorphic systems.

Recent advances in neuromorphic hardware have focused on enhancing scalability, enabling chips to support larger and more complex networks – for example, with the adoption of improved memory architectures and

3D-stacked designs to overcome data bandwidth limitations<sup>[12] [13]</sup>. This also reduces latency and enables real-time processing of high-dimensional data<sup>[14] [15]</sup>.

Energy efficiency remains a primary objective as temporal sparsity and event-driven computation minimises unnecessary activity, significantly reducing power consumption. For Edge AI devices and advanced memory technologies such as memristors and resistive RAM (ReRAM), this represents a promising evolution. Moreover, the combination of SNN accelerators with energy-harvesting technologies could contribute to the diffusion of energy-autonomous systems, enabling devices to operate indefinitely in remote or resource-constrained environments; in IoT applications, this could represent a game changer.

Another trend is the integration of SNNs with traditional deep learning frameworks, creating hybrid architectures that combine the strengths of both paradigms: these systems can switch between continuous and event-driven computation, optimising workloads dynamically for a wide range of applications.

The next generation of SNN accelerators will require novel materials, enhancing computational density, such as phase-change memory and memristors, to replicate synaptic functions with greater efficiency. They will allow the simulation of more biologically accurate neural dynamics, while a futuristic evolution could involve the fusion of quantum computing with neuromorphic principles. Such quantum systems, with their inherent parallelism and superposition capabilities, offer a new dimension for processing spike-based computations. Hybrid quantum-SNN architectures could also accelerate learning and inference processes, tackling optimisation problems that are currently infeasible with classical systems<sup>[16]</sup>.

From an architectural perspective, SNN accelerators will include cognitive-level processing, enabling chips to perform higher-order tasks such as reasoning, abstraction and multi-task learning. By incorporating hierarchical and modular architectures, these systems will approximate the layered complexity of biological brains, making them suitable for applications in AGI.

#### 4.2 RISC-V based accelerators

RISC-V is very frequently adopted to develop Edge AI accelerators due to their flexibility and modularity, which enables the customisation of processors tailored to specific workloads and applications. Current RISC-V based accelerators are characterised by their ability to balance performance and power efficiency, crucial for Edge AI systems operating in resource-constrained environments – such as IoT devices, autonomous sensors and robotics. For example, the integration of domain-specific extensions within RISC-V cores, enabling accelerators to handle specialised tasks such as matrix multiplications, Convolutional Neural Network (CNN) inference, and vectorised computations, have been adopted to develop lightweight accelerators with a reduced energy consumption profile while maintaining high throughput in machine-learning tasks. A practical implementation is the Parallel Ultra-Low Power (PULP) platform, which builds on RISC-V cores to deliver ultra-low power AI solutions. The PULP project emphasises fine-grained parallelism and energy-efficient computation, leveraging custom extensions for machine-learning inference, to enable efficient data movement and computation, key factors for Edge AI tasks.

<sup>12</sup> Indiveri, G., & Liu, S. C. (2015). "Memory and information processing in neuromorphic systems." Proceedings of the IEEE, 103(8), 1379–1397.

<sup>13</sup> Prezioso, M. et al. (2015). "Training and operation of an integrated neuromorphic network based on metal-oxide memristors." Nature, 521(7550), 61–64.

<sup>14</sup> BrainChip. (2022). "Akida: Neuromorphic Processing at the Edge." [white paper].

<sup>15</sup> Zidan, M. A. et al. (2018). "The future of electronics based on memristive systems." Nature Electronics, 1(1), 22–29.

<sup>16</sup> Marković, D. et al. (2020). "Physics for neuromorphic computing." Nature Reviews Physics, 2(9), 499–510.

A different approach adopts vectorised processing units in RISC-V accelerators to process multiple data elements simultaneously, significantly improving the performance of neural network operations. For example, the RISC-V Vector Extension (RVV) standard enables scalable vector processing, making it particularly effective for handling the parallel nature of deep learning algorithms.

Emerging trends emphasise the use of heterogeneous architectures, where RISC-V cores work synergistically with specialised AI processing units. This approach leverages the programmability of RISC-V for control tasks while delegating computation-heavy operations to AI-specific accelerators. Such architectures enable a more efficient division of computing load, reducing power consumption and latency in real-time applications.

The integration of approximate computing is another frontier for these accelerators, paving the way for accelerators that strike a balance between accuracy and efficiency. By exploiting the inherent tolerance of AI algorithms to computational noise, approximate computing techniques reduce precision levels in arithmetic operations, thereby enhancing energy efficiency.

Moreover, the combination of RISC-V with emerging memory technologies like ReRAM and 3D-stacked memory is anticipated to address the memory bottleneck in AI workloads. These technologies enable faster and more energy-efficient data access, which is critical for large-scale AI models at the edge. Future accelerators may integrate these memory systems with RISC-V cores to enhance the processing of data-intensive tasks.

Another promising direction involves the use of RISC-V in neuromorphic computing, where accelerators are designed to emulate biological neural networks. By leveraging RISC-V's modularity, developers can implement spiking neural network accelerators that combine biological plausibility with energy efficiency.

## 4.3 Photonic/optical-based accelerators

Photonics and optical technologies offer an alternative for high-speed and efficient AI tasks. These technologies exploit the unique properties of light, such as high bandwidth, low latency and minimal energy dissipation, to perform computations that would be prohibitively slow or power-intensive on conventional electronic hardware. As Edge AI applications demand compact, energy-efficient systems capable of processing massive data streams in real time, photonics-based accelerators are emerging as a promising solution.

At the forefront of this field are photonic neural networks, which leverage optical components such as waveguides, modulators and resonators to execute AI workloads, drastically reducing latency and power consumption. These solutions use optical interference to compute in parallel and efficiently perform matrix multiplications<sup>[17]</sup>.

Silicon photonics, a mature and scalable technology, has enabled the integration of photonic accelerators into edge devices, combining the precision of photonics with the practicality of CMOS-compatible manufacturing, paving the way for cost-effective deployment. In this context, the use of optical memory, such as phase-change memory, allows the storage of data in light-sensitive materials, enabling ultra-fast read/write cycles. Similarly, optical interconnects eliminate bottlenecks associated with electronic data transfer, allowing accelerators to handle high-throughput tasks with minimal latency. These innovations are particularly beneficial for edge scenarios involving real-time data analytics and autonomous decision-making<sup>[18]</sup>.

Photonics-based AI accelerators present several challenges, specifically in the integration of optical and electronic components, as hybrid systems often encounter inefficiencies at the interface. Additionally, scaling photonic architectures for more complex neural networks requires innovations in device miniaturisation and photonic circuit design. Co-packaged photonic processors, where optical and electronic components share a common substrate,

<sup>17</sup> Shen, Y., et al. (2017). "Deep learning with coherent nanophotonic circuits." Nature Photonics, 11(7), 441–446.

<sup>18</sup> Feldmann, J., et al. (2021). "Parallel convolutional processing using an integrated photonic tensor core." Nature, 589(7840), 52–58.

will eliminate inefficiencies at the interface, enabling seamless communication between light and electrons. This will be crucial for scaling photonic accelerators to support large, complex neural networks in edge devices.

Beyond these advances, the future of photonic accelerators could lie in the use of novel materials such as two-dimensional semiconductors and meta-surfaces to enhance the efficiency and scalability of photonic devices. These materials allow for more compact, denser (nanoscale precision) and energy-efficient photonic circuits, making them suitable for deployment in constrained edge environments.

Quantum photonics is another transformative direction, as it offers the potential to harness quantum phenomena such as superposition and entanglement for AI computations. Hybrid quantum-photonic systems could drastically enhance the parallelism and speed of AI accelerators, particularly for tasks such as optimisation and pattern recognition.

Merging neuromorphic and photonics could also be an alternative, with photonic implementations in SNNs, which could enhance tasks requiring temporal data processing, such as speech recognition and autonomous navigation.

## 4.4 Biological processors

Biological processors and organoids represent an emerging frontier in AI hardware, where biological systems are employed to perform computation. This paradigm diverges significantly from traditional silicon-based processors, leveraging the unique properties of biological materials, such as adaptability, energy efficiency and self-organisation. As Edge AI demands compact and efficient systems capable of real-time processing, biological processors and organoids present promising solutions by mimicking the unparalleled computational capabilities of biological brains.

Biological processors, particularly those based on synthetic biology and engineered genetic circuits, use living cells or biomolecules to process inputs and generate outputs. For example, bacterial cells can be programmed to function as logic gates, responding to chemical signals with specific outputs. These systems demonstrate the potential for massive parallelism, as billions of cells can work simultaneously to process complex datasets. Recent advances highlight the development of molecular logic circuits capable of performing computations similar to traditional electronics, but with far lower energy requirements.

Organoids, three-dimensional cellular structures that mimic the architecture and functionality of the brain, represents another alternative for neuromorphic computation. Brain organoids, in particular, are cultivated from stem cells to replicate certain aspects of neural processing. Recent research has demonstrated the ability of brain organoids to exhibit spontaneous electrical activity, resembling primitive forms of neural computation. Organoids hold potential for Edge AI, as they can perform real-time processing in a biologically realistic manner, with minimal energy consumption.

While these technologies are still in their infancy, their unique features make them well-suited for Edge AI applications, especially as biological processors excel in energy efficiency and adaptability, qualities critical for remote or autonomous systems. Organoids, on the other hand, offer unparalleled parallelism and plasticity, enabling them to learn and adapt to new data, much like biological brains.

Despite these advantages, challenges remain. Biological systems are inherently less predictable than electronic circuits, and their integration with existing AI infrastructures poses significant hurdles. Additionally, scaling these technologies for practical applications requires breakthroughs in bioengineering and computational frameworks.

One promising direction is the development of hybrid bioelectronic systems, where biological components interface seamlessly with traditional electronics. Advances in bioelectronic interfaces are enabling real-time

<sup>19</sup> Qian, L., et al. (2011). "Neural network computation with DNA strand displacement cascades." Nature, 475(7356), 368–372.

communication between living cells and silicon-based processors. This hybrid approach combines the adaptability of biological systems with the precision and scalability of electronics, creating versatile platforms for Edge AI.

Organoids are also being adopted in neuromorphic computing, as by cultivating larger and more complex brain organoids researchers aim to replicate higher-order cognitive functions such as decision-making and pattern recognition. Recently, organoids have been trained to control robotic systems, suggesting their potential for real-time autonomous operations at the edge.

Furthermore, synthetic biology is driving innovations in the programmability of biological processors. Techniques such as CRISPR-Cas9 gene editing are enabling the design of genetic circuits with greater complexity and specificity. With this technology, engineered bacterial systems have been able to process spatial and temporal data, opening new possibilities for applications in environmental monitoring and healthcare.

## 4.5 Chiplets

**Chiplets** are small integrated circuit (IC) die that are designed to work together within a single package to form a complete system. Instead of having one large, monolithic die, a system is split into multiple smaller die, or chiplets, each performing specific functions. These chiplets are interconnected using advanced packaging technologies to create a cohesive system-on-a-chip (SoC).

This technology promises enhanced performance, flexibility, scalability and power efficiency, as well as improved yield and cost-reduction due to the modularity it enables for SoCs. This modularity enables the reuse of chiplets and their optimisation for specific tasks. All these advantages make chiplets an interesting approach for many markets such as IoT devices or automotive applications.

Naturally, they are also applicable to Edge AI aspects of these areas. However, before chiplets can find wide-spread adoption, challenges such as standardisation, power distribution management and the linking of different chiplets need to be resolved. To tackle these issues, groups such the ASRA group in Japan and the IMEC automotive chiplet program in Europe were formed.

## 4.6 In-memory computing (memristive technologies)

In-memory computing integrates computation and data storage within the same physical components, significantly reducing the need to transfer data between separate processors and memory units. Memristive technologies – including spin-orbit torque MRAM (SOT-MRAM), phase-change RAM (PCRAM) and oxide-based resistive RAM (OxRAM) – enable memory cells to perform logic or analogue computations directly. By substantially reducing data movement, in-memory computing greatly enhances the speed and energy efficiency of AI inference. Traditional deep learning hardware often spends more time and energy moving data (weights and activations) between off-chip dynamic random-access memory (DRAM), on-chip static random-access memory (SRAM), and computational units than executing arithmetic operations [20].

Emerging technologies such as SOT-MRAM, PCRAM and OxRAM integrate memory and processing functions, significantly reducing data transfer latency. By minimising bottlenecks between the CPU and memory, these architectures boost inference speed – an essential advantage for real-time AI applications. Their low-latency performance makes them especially well-suited for Edge AI, where fast on-device processing is critical.

## 4.7 ASICs, SoCs and microcontrollers

Application-specific integrated circuits (ASICs) and AI-centric SoCs are custom-engineered to deliver highly efficient deep learning inference. Unlike general-purpose CPUs or GPUs, which are designed for a wide range of tasks, these chips incorporate specialised circuits such as tensor engines and neural processing units, components that are finely tuned for the types of matrix operations and neural network computations that underpin modern AI models.

The result of this specialisation is a significant boost in both performance and energy efficiency. ASICs and SoCs can achieve extremely high throughput – often measured in trillions of operations per second (TOPS) – while maintaining a low power footprint. For instance, a neural processing unit embedded in a smartphone can perform several TOPS of inference while consuming only a few hundred milliwatts of power, a level of efficiency that conventional CPUs or GPUs cannot sustain. However, this high level of optimisation comes with a trade-off: these chips are typically limited in flexibility, and are best suited for specific tasks rather than general-purpose computing.

In many AI systems, particularly those operating at the edge, microcontrollers (MCUs) are integrated alongside ASICs or within SoCs to handle tasks that require low power and real-time responsiveness. While MCUs lack the processing muscle for intensive inference, they are essential for coordinating sensor input, triggering inference operations, and managing communication between different components of the system. In certain ultra-low power scenarios, such as TinyML applications, even simple neural networks can be deployed directly on microcontrollers, enabling basic AI functionality directly on the device without relying on cloud resources.

As AI continues to expand into embedded and autonomous systems, ASICs and SoCs are becoming increasingly vital. Their ability to deliver high-performance, low-latency inference makes them well-suited for demanding applications such as voice recognition, computer vision, autonomous vehicles and industrial automation.

#### 4.8 FPGAs

Field programmable gate arrays (FPGAs) provide a unique and powerful platform for accelerating AI models by offering reconfigurable hardware fabrics that enable massive parallelism. At their core, FPGAs consist of an array of configurable logic blocks interconnected in a way that allows designers to create custom datapaths and computational units. This flexibility is particularly valuable for AI workloads, where operations such as multiply-accumulates, adders and control logic can be spatially mapped and optimised to match the structure of a given neural network.

Unlike ASICs, which are fixed-function chips tailored for specific tasks, FPGAs can be reprogrammed to support new or evolving model architectures. This reconfigurability makes them ideal for AI applications that require frequent updates or experimentation, such as in Edge AI deployments or during the prototyping phase of development. Engineers can fine-tune hardware characteristics – including dataflows, memory hierarchies and bit-widths – to match the demands of each model, thereby enhancing both performance and efficiency.

One of the key strengths of FPGAs lies in their ability to adapt to a wide range of AI models while maintaining moderate power consumption. Their architecture supports extremely low-precision computing, with some designs utilising quantisation down to just one or two bits. This not only accelerates computation but also drastically reduces power usage – an essential advantage for power-sensitive environments.

As the landscape of AI continues to evolve rapidly, FPGAs offer the agility and customisation required to stay aligned with the latest advances, making them a compelling choice for developers building cutting-edge adaptive AI solutions.

## 4.9 ECHO gateway for AI processing

A standardised, automated interface framework enabling seamless chip-to-cloud (such as machine-to-machine) communication is essential. Automated access from Edge CHip to clOud (ECHO) should enable fast AI processing on the cloud without any access to external world to offer trustworthiness, and ensure privacy and secured AI processing.

Bridging the gap between edge devices and cloud infrastructure at the hardware level minimises the fragmentation of operating systems and communication protocols, as highlighted by a CEUR-WS paper <sup>[21]</sup>. To maintain a secure data flow from edge to cloud, direct hardware-level access within cloud platforms – such as AWS, IONOS and Azure – must be enabled via secure application programming interfaces (APIs), independent of application-specific knowledge. For futuristic multi-core edge processors, message queuing telemetry transport (MQTT) and constrained application protocol (CoAP) are not efficient when there is a hardware-based API communication as then channels are scalable, and it enables a priority-based channel for uplink and downlink (also easy to port on 5/6G).

To mitigate potential security threats, the system must implement end-to-end encryption, strong authentication mechanisms, zero trust, a time stamp, and enforce consistent security policies across the entire datapath – from edge devices to cloud infrastructure. This architecture ensures that no intermediate software layer can access or tamper with the data during transfer, enabling secure AI training and inference in the cloud.

To address the different application needs, the cloud can offer improved scalability and hardware-level flexibility to accommodate a wide range of application requirements, facilitating seamless ECHO integration<sup>[22]</sup>.

A key benefit of this hardware-centric gateway approach is reduced latency and faster AI model training. It also supports in-memory computing and facilitates the integration of deep neural networks directly within data pipelines, enabling AI processing closer to the source without overloading higher-tier AI accelerators<sup>[23]</sup>.

Ultimately, this architecture reduces dependency on software configuration, minimises manual handovers, and simplifies secure cloud access – paving the way for highly efficient and secure AI-driven systems.

<sup>21</sup> Stanko, A. et al. (2024). "Artificial intelligence of things (AIoT): Integration challenges, and security issues" (https://ceur-ws.org/Vol-3842/paper6.pdf).

<sup>22</sup> See PwC, (2024) "2024 cloud and AI business survey." (https://www.pwc.com/us/en/tech-effect/cloud/cloud-ai-business-survey.html).

<sup>23</sup> Jhang et al. (2021) "Challenges and trends of SRAM-based computing-in-memory for AI edge devices." IEEE Transactions on Circuits and Systems. 68(5). 1773–1786 (https://ieeexplore.ieee.org/document/9382915).

#### 4.10 Conclusion

There is much evidence of a shifting paradigm toward Edge AI. Traditional DNNs dominate high-performance cloud-based applications but face scalability issues at the edge due to high power and computing demands. There is a growing need for energy-efficient, real-time AI solutions closer to data sources, which is fuelling innovation in edge-focused hardware.

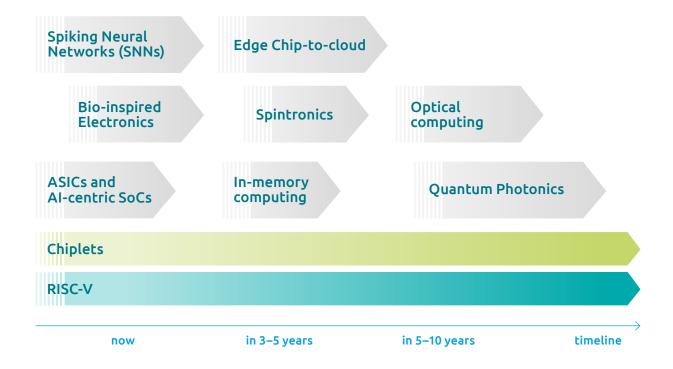

Figure 4.1: Timeline for the emerging hardware architectures

SNNs, inspired by biological neurons, offer ultra-low-power and real-time processing, particularly suitable for robotics, time-series data and sensory applications. Neuromorphic chips such as Intel's Loihi and IBM's TrueNorth showcase the potential of on-chip learning and energy efficiency. However, challenges remain in training complexity and hardware specialisation.

RISC-V's modularity makes it ideal for customising AI accelerators for edge devices. Platforms like PULP and vector extensions (RVV) enable efficient processing of ML workloads. The integration of heterogeneous computing and approximate computing further enhances power efficiency and performance in constrained environments.

Optical computing offers significant advantages in speed, parallelism and energy efficiency. Photonic neural networks and silicon photonics reduce latency and power usage, making them well-suited for high-throughput edge applications. Future advances will rely on hybrid photonic–electronic systems, new materials, and potentially quantum photonics for extreme acceleration.

Chiplets enable flexible, scalable, and cost-effective AI hardware by modularising specific functions within a chip package. Their reuse and task-specific optimisation make them ideal for Edge AI in domains including IoT and automotive. Widespread adoption depends on overcoming standardisation and integration challenges.

Although they are still experimental, biological computing systems (eg, brain organoids and synthetic bio-processors) show promise for ultra-energy-efficient, adaptive AI at the edge. Hybrid bioelectronic interfaces are also emerging, with the aim of combining biological adaptability with electronic control for the next-generation of intelligent systems [24].

In-memory computing technologies (eg, SOT-MRAM, PCRAM, OxRAM) drastically reduce data movement, enhancing speed and power efficiency. This is particularly important for edge devices that require fast, local AI inference. These architectures address memory bottlenecks and support real-time AI processing.

ASICs and AI-centric SoCs are highly specialised for deep learning inference, offering maximum performance and energy efficiency for specific tasks. In contrast, FPGAs provide a reconfigurable platform that trades some efficiency for flexibility, making them ideal for evolving or frequently changing AI models. The choice between them reflects a trade-off between performance optimisation and hardware adaptability.

The ECHO architecture provides a highly efficient and secure foundation for next-generation AI systems. It simplifies cloud access, minimises manual configuration, and delivers the flexibility and scalability needed to accommodate diverse application requirements – ultimately setting a new standard for secure, hardware-level chip-to-cloud integration.

<sup>24</sup> Boufidis, D. et al. (2025) "Bio-inspired electronics: Soft, biohybrid, and 'living' neural interfaces." Nature Communications. 16 (https://www.nature.com/articles/s41467-025-57016-0).

## 5 Challenges, Constraints and Limitations Drive Innovation in Hardware Solutions for Edge AI

As Edge AI continues to evolve, it brings with it a unique set of challenges, constraints and limitations that demand a fresh wave of innovation in hardware design. This chapter explores the pressing technical, environmental, computational and specific AI model-related hurdles that require innovation in Edge AI hardware solutions.

## 5.1 Edge device constraints

Deploying AI algorithms on edge devices presents several constraints that must be carefully managed to ensure optimal performance.

- Processing power and speed: Al algorithms require substantial computational resources to execute within

acceptable timeframes. Edge devices often have limited processing capabilities, making it challenging to

run complex models efficiently. Specialised hardware accelerators, such as neural processing units (NPUs),

can enhance performance by offloading Al-specific tasks from general-purpose CPUs.

- Available memory: Sufficient onboard memory is essential for temporarily storing and retrieving data during AI model execution. The size and speed of this memory directly impacts processing speed, energy consumption and overall efficiency. Techniques such as model quantisation and pruning can reduce memory requirements, enabling the deployment of AI models on devices with constrained resources. AI models must be stored on the device, and storage limitations can restrict the complexity and size of deployable models. Efficient model compression methods are crucial to fit models within the storage constraints of edge devices without significantly compromising performance.

- **Energy consumption:** Processing and data movement in AI tasks consume power, and larger models typically lead to higher energy consumption, reducing device autonomy. Energy-efficient model architectures and hardware accelerators can mitigate this issue by optimising power usage during inference.

- Processing support: Traditional processors (CPUs or microcontrollers) often complement AI accelerators

in edge devices, handling tasks that are not well-suited for specialised hardware. However, this

collaboration can further reduce device autonomy due to increased energy consumption. Balancing the

workload between general-purpose and specialised processors is essential to maintain efficiency.

- Connectivity: Edge nodes are typically connected to external resources, typically to send sensory

data or receive commands, and to interact with cloud resources. However, they suffer from unreliable

connectivity, and can also be unable to deliver the data rates and latency required by the application.

Introducing connectivity management and local AI capabilities (in particular with distributed or split AI

approaches) significantly increases the robustness and performance of the deployed application.

- Hardware deterioration: Edge devices are exposed to a much wider range of sources of hardware deterioration (including different kinds of weather) than processing hardware in cloud servers. The deterioration of the underlying hardware leads to a reduction in the performance of AI models deployed on edge devices. Hence, it is essential that Edge AI models are robust and flexible, and that edge application systems include mechanisms for performance monitoring and updates to deal with the deterioration, which will increase the lifetime and sustainability of AI-based edge products.

- Security and safety: Edge devices are often much easier to access than a cloud server. This makes them

vulnerable to wider range of attacks, especially physical ones. Hence, AI models that are used for safetycritical processes need to be deployed on certified edge hardware with security and safety components

and mechanisms.

Device resource sharing: The adoption of multiple AI models of the same device generally involves

the concurrent use of its limited recourses, reducing their availability and negatively impacting on

performances.

Addressing these constraints requires a holistic approach, combining hardware advancements with software optimisation techniques to enable effective AI deployment on edge devices.

## 5.2 Edge model and application constraints

Software—hardware co-design is essential for Edge AI, tightly integrating hardware capabilities with software demands to optimise efficiency, performance and power usage – critical aspects for edge applications. Edge devices typically face stringent power constraints; co-design ensures software algorithms leverage hardware strengths to significantly reduce energy consumption. By tailoring hardware acceleration specifically to AI models, co-design enables faster, responsive and real-time processing.

Aligning software requirements with hardware execution minimises data movement and latency, which is crucial for real-time performance. Additionally, this approach supports adaptable and future-proof hardware architectures that can evolve alongside emerging software techniques and increasing AI model complexity. Ultimately, software—hardware co-design effectively bridges algorithm innovation and hardware functionality, creating efficient, powerful and responsive Edge AI solutions.

#### Optimising AI models and applications for edge devices involves addressing several key constraints.

- Model size: Large models demand more computational power and memory, which can lead to slower

operations on resource-limited edge devices. Techniques such as model pruning and quantisation can

reduce model size, enhancing performance without significantly compromising accuracy.

- Model accuracy and precision: The level of precision used in data representation affects hardware

resource requirements, and consequently the performance and accuracy of AI models. Balancing

precision and resource utilisation is crucial for efficient edge deployment.

- Model architecture: The design and parameter interconnections within a neural network influence computational efficiency, memory usage and processing speed. Selecting architectures optimised for edge environments is essential for effective deployment.

- Model training and inference: In the context of Edge AI, it is important to differentiate between training and inference (deployment). Typically, AI models undergo resource-intensive training processes in cloud environments, where substantial computational resources are available. Once trained, these optimised models are deployed to edge devices, where inference occurs. This separation ensures computationally demanding training tasks do not burden resource-constrained edge hardware, while still enabling efficient, real-time, on-device AI. Training models directly on low-power devices is still a cutting-edge area, one that comes with a host of challenges both technical and practical; however, with breakthroughs in software and data-centric strategies, federated learning and hardware, it is becoming more feasible.

- Application speed requirements: Edge devices may struggle to meet the speed demands of applications

due to resource constraints, affecting their ability to ingest data and perform inference in a timely manner.

Optimising both hardware and software is necessary to achieve the required performance levels.

- Data volume versus resource availability: Handling large datasets or high-resolution inputs can quickly

exceed the available resources of edge devices, hindering application performance. Implementing data

compression and efficient data-handling strategies can mitigate this issue. However, edge devices may

have limited or intermittent access to labelled data (essential for supervised training), and this has led to